日本欲重返“芯片制造霸主”之位 拨款约39亿美元驰援“日版台积电”

智通财经APP获悉,日本政府部门批准向有着“日版台积电”称号的日本芯片制造商Rapidus Corp.提供高达5900亿日元(大约39亿美元)的巨额补贴,为其赶超台积电、三星电子等芯片制造领域领导者的雄心提供更多资金。据了解,来自日本的造芯新势力Rapidus成立于2022年,该芯片制造商的成立得到了日本政府的高额财政支持,同时该新锐芯片制造商也得到了一些日本大型公司的鼎力支持,这些公司包括丰田、索尼、NEC、NTT、软银以及电装等日本顶级公司。

日本经济产业大臣斋藤健(Ken Saito)接受媒体采访时表示,这笔额外的资金援助将帮助Rapidus购买更加先进的芯片制造以及先进封装设备,并开发先进的后端芯片制造与封装工艺。在此之前,这家成立仅仅19个月的芯片制造新势力已经获得了高达3300亿日元的日本政府资金支持,希望未来在位于日本最北部的北海道地区大规模生产2nm级别的先进制程芯片,并且在其他先进制程领域与有着“芯片代工之王”称号的台积电(TSM.US),以及韩国的芯片制造巨头三星电子(Samsung Electronics Co.)在芯片制造领域进行竞争。

斋藤周二在东京举行的例行新闻发布会上强调:“Rapidus正在加速研发的下一代半导体先进制程是该行业重要的前沿技术,将决定日本工业和经济增长的未来前景。”“因此本财年对Rapidus来说极为重要。”

在日本政府拨款39亿美元大力支持Rapidus发展的这一消息传出后,日本的众多半导体设备供应商纷纷上涨,其中东京电子(Tokyo Electron Ltd.)早盘上涨3.2%,朝着历史最高点位奔去。相比于应用材料和泛林这两大来自美国的半导体设备巨头,东京电子在涂覆机以及显影机(Coater/Developer)领域具有非常高市占率。东京电子在ALD、CVD、PVD、RTP、CMP、刻蚀和离子注入设备等领域则为应用材料最强竞争对手。

日本“梭哈”芯片制造领域,向全球展现“芯片强国战略”

在不到三年的时间里,日本首相岸田文雄领导的政府已经雄心勃勃地制定高达4万亿日元(大约 270 亿美元)的援助计划,来振兴日本国内芯片制造行业,同时也旨在帮助日本经济重新回到政府和央行所寻求的正增长周期。此次拨出的对于Rapidus的额外资金支持乃4万亿日元的一部分,目的是通过大力扶持Rapidus来全面恢复日本昔日的芯片制造领军者地位。

日本首相岸田文雄计划向芯片制造商和私营部门提供大约10万亿日元的财政支持。除了扶持来自日本的造芯新势力Rapidus,日本政府还向台积电在日本南部熊本的第一家工厂投资数十亿美元。据悉,日本政府还将向台积电位于熊本的第二家大型芯片工厂提供至多7320亿日元(约48.6亿美元)补贴,该工厂拟于2024年底开始建设,聚焦于5nm等高端制程。

日本政府还计划向美国存储巨头美光科技(MU.US)在日本广岛工厂的扩建项目投资了数十亿美元,以生产先进DRAM。

日益紧张的全球地缘政治局势正促使世界各国政府建立或者扩大国内的芯片制造规模,尤其是制造AI芯片等高性能计算芯片的能力。芯片制造领域对于一个国家的AI级数据中心汽车、发电厂、武器系统以及消费电子产品的运行至关重要。除了日本,美国和欧盟等发达地区同样承诺向芯片制造商提供数十亿美元补贴,但在许可和补贴分配方面的过于拖延阻碍了芯片工厂建设计划。

对于在日本国内芯片制造领域的重磅投资项目,日本政府能够迅速发放最高达50%的建设成本补贴,因此,这一高效率的巨额补贴比例吸引台积电、美光和三星电子等行业领导者赴日建厂,加之日本在半导体设备和半导体高端原材料领域堪称全球领导者,在该领域坐拥东京电子、东京应化工业以及信越化学等巨头,芯片制造巨头更愿意前往日本建设工厂。

日本北部的北海道岛和南部的熊本已经有不少信息表明,新建成的芯片制造工厂开始影响当地经济,并阻止人们涌向东京寻求更好的工作和教育。岸田文雄还计划在日本私营部门的支持下,将芯片产业的财政支持提高到10万亿日元(约670亿美元)。

日本政府倾尽全力扶持“日版台积电”Rapidus,力争未来斩获2nm制程的领军地位

日本政府此前雄心勃勃地在北海道启动Rapidus 2nm级别先进制程项目,计划在2027年大规模量产最先进的2nm芯片,寻求日本在高端芯片市场领跑全球。

据媒体报道,Rapidus正在与日本顶级的纳米技术和材料领域的研究人员进行合作,以缩小与台积电在最尖端芯片制造技术方面的差距。台积电多年来在全球芯片代工领域中占据着最大份额,仅次于其份额的竞争对手三星电子多年来一直难以赶上,尤其是在5nm以下的先进制程领域份额与台积电差距非常大。

据日本经济产业省最新披露的数据,日本政府新批准的补贴中有5,365亿日元将用于为Rapidus Chitose大型工厂的试验生产线安装高端半导体设备、招募来自IBM的顶尖芯片研究人员、缩短周转时间和建立庞大的生产控制系统。

进军2nm这一当前最前沿制程领域,意味着需要大批量采购所需的高端半导体设备,比如造芯必须具备的光刻机、刻蚀设备以及薄膜沉积等高端半导体设备,并且2nm制程对于设备有着更高的功率和精准度要求,可能导致在光刻、刻蚀、薄膜沉积、多层互连以及热管理等环节有更高的技术要求,因此有可能需要比常规制程高端得多的制造和测试设备来满足这些要求。

比如,对于台积电以及Rapidus正在研发的2nm及以下节点技术而言,阿斯麦high-NA EUV光刻机至关重要。相比于阿斯麦当前生产的标准EUV光刻机,主要区别在于使用了更大的数值孔径,High-NA EUV技术采用0.55 NA镜头,能够实现8nm级别的分辨率,而标准的EUV技术使用0.33 NA的镜头。因此,这种新NA技术能够在晶片上打印更小的特征尺寸,对于2nm及以下芯片的制程技术研发至关重要。

剩余的大约535亿日元,Rapidus则计划用于开发媲美台积电的chiplet先进封装技术。随着在硅片上压缩更多晶体管的成本越来越高,chiplet先进封装是一个吸引全球芯片公司关注的领域。在我们所处的“后摩尔时代”(Post-Moore Era),芯片先进制程突破面临极大难度(如量子隧穿效应以及开发成本指数级增长),加之逐渐迈入AI时代以及万物互联趋势愈发明显,多种任务带来的算力需求可能激增,比如深度学习任务、训练/推理、AI驱动的图像渲染、识别等。这些任务对硬件性能要求都非常高,这意味着像PC那样单独集成的CPU或GPU已经无法满足算力需求。

因此,Chiplet先进封装应运而生。Chiplet封装技术可以使不同的GPU模块,或者CPU、FPGA、ASIC芯片等在同一个系统中协同工作,最大化地高效调度各类型芯片算力,以提供更大规模的并行计算能力。台积电当前凭借其领先业界的2.5D/3D先进封装吃下市场几乎所有5nm及以下制程高端芯片封装订单,并且先进封装产能远无法满足需求,英伟达H100供不应求正是受限于台积电2.5D级别的 CoWoS封装产能。

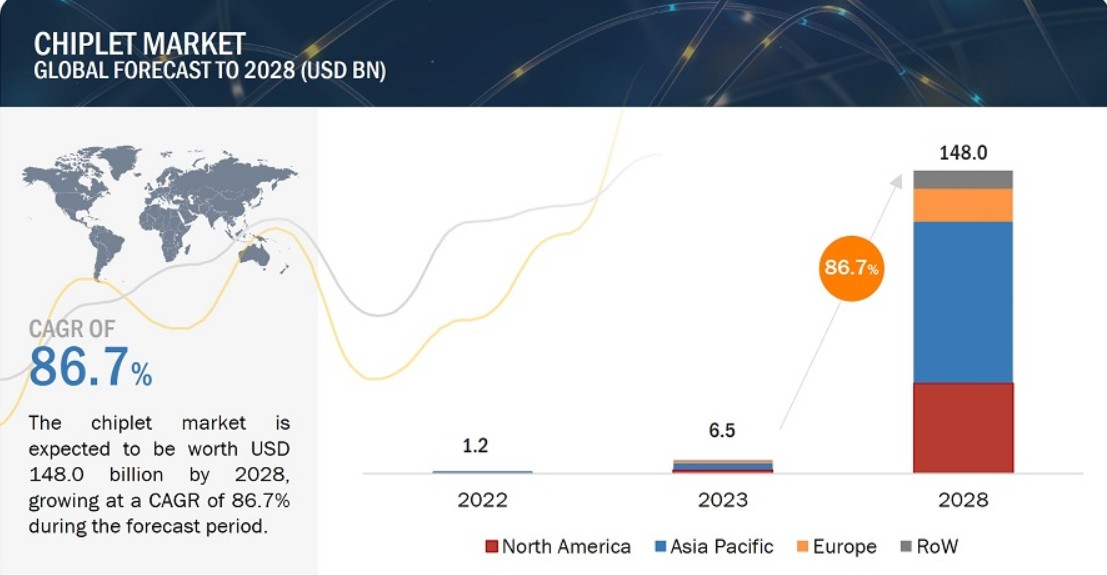

IDC预计至2024下半年,台积电CoWoS产能有望大幅增加约130% 。另一研究机构Markets And Markets最新研究显示,覆盖GPU、CPU、FPGA等芯片的Chiplet先进封装成品、先进封装技术(2.5D/3D、SiP、WLCSP、FCBGA和Fan-Out等)的Chiplet市场总额有望于2028年达到约1480亿美元,年复合增速(CAGR)高达惊人的86.7%。根据该机构测算,2023年Chiplet市场总额可能仅为65亿美元。

日本经济产业大臣斋藤健表示,日本三十多年来的经济停滞和国际竞争力逐渐丧失,部分原因是缺乏对芯片在全球科技产业、数字化、脱碳和经济安全领域的重要理解。他强调:“我们可以毫不夸张地说,芯片是这个国家和世界工业的最核心基础。”

据了解,日本政府“芯片强国战略”的主要目标是力争到2030年将日本国内的国产芯片销售额增加两倍,达到15万亿日元左右。日本政府力争在2027年,推动政府支持的这家有着“日版台积电”称号的芯片制造商Rapidus能够量产2nm芯片,应用于人工智能、自动驾驶以及量子计算等最前沿领域。此前在东京举行的联合发布会上,AI初创企业Tenstorrent宣布将其AI芯片的部分设计授权给日本政府支持的Rapidus,并将共同设计芯片。Tenstorrent CEO则是大名鼎鼎的硅谷传奇人物、Zen架构之父Jim Keller。

扫码下载智通APP

扫码下载智通APP