汽车芯片走到分岔口

当前,在电动化、智能化、网联化和共享化等“新四化”趋势推动下,汽车已经成为“轮子上的数据中心”,汽车半导体用量迅速提升。预计到2030年,高端汽车物料清单中,芯片比重将从当前的4%左右提升至20%以上。

随着汽车电动化和智能化进程的加快,汽车对新一代芯片的要求也在不断提升。

过去一个普通的单片机就可以应付整车的电子控制系统,而如今随着辅助驾驶、语音识别、多媒体、车联网...等新兴场景的快速崛起,对芯片计算性能提出了更高的要求。

汽车芯片从原来通用型、分散化的单一功能芯片快速转向集成化的多功能SoC芯片。比如,在智能座舱领域,CPU算力用于提高任务处理能力,还需要GPU算力来处理视频等非结构化数据,高效的AI算力来满足智能化交互体验要求,以提升人机交互体验。

这些不同的IP核组成了性能强大的SoC。而在SoC的背后,不同的制程工艺在一定程度上决定了硬件性能的上限。

尤其是在“软件定义汽车”的趋势下,芯片硬件作为运行软件的基础,需要为未来OTA等迭代升级预留空间。

因此,汽车芯片的制程工艺变得至关重要。

为满足这些要求,业内正在加速研发性能更强的芯片,先进制程越来越多地成为满足汽车芯片应用的重要筹码之一。

今年7月,台积电欧洲总经理Paul de Bot在第27届汽车电子大会上表示,汽车行业的芯片和采购芯片的方式都变得越来越复杂。

长期以来,汽车行业一直被认为是技术落后者,只注重落后工艺,但实际上,汽车行业在2022年开始使用5nm工艺—— 距离5nm进入量产仅两年。

台积电强调:“不可能为汽车行业预留闲置产能,建议汽车制造商尽快开始计划转向先进节点。”

汽车芯片,迈向先进制程

在传统车用半导体制备中,由于汽车本身空间较大,对集成度的需求没有手机等消费电子紧迫。加上半导体元器件主要集中在发电机、底盘、安全、车灯控制等领域,对算力没有太高的要求。以往,汽车芯片大多采用40nm及以上的成熟工艺制程,跟消费电子芯片在工艺上差了不止一个量级。

但在汽车智能化的革命浪潮之下,随着智能座舱、自动驾驶水平的提升,都依赖大算力、低功耗芯片的支持,24nm乃至48nm制程工艺的车规级芯片显然已经跟不上产业的快速转型。

汽车芯片正由过去工艺制程相对落后、量大价低的行业洼地,摇身一变成为芯片行业高精尖技术的应用先锋,芯片企业争相抢占的技术制高点。

这意味着,汽车芯片将不再与成熟工艺制程绑定,先进工艺制程将成为芯片行业技术创新的制高点。

车规级芯片根据功能分为计算控制芯片、存储芯片、功率半导体、传感器芯片等几大类。从芯片工艺制程来看,不同汽车芯片对工艺要求存在较大差异。MCU主要是依靠成熟制程,全球约70%的MCU生产来自台积电;而智能座舱、自动驾驶及AI芯片等主控芯片出于性能和功耗考虑,持续追求先进制程,高级别自动驾驶正在推动汽车算力平台制程向7nm及以下延伸。

在此趋势下,催生了高通、英伟达、英特尔、联发科等高性能计算玩家进入车用市场,推动汽车算力平台制程向7nm及以下延伸。

从趋势上看,智能座舱和自动驾驶被视为未来的“机会风口”之一,也是制程工艺竞争最为激烈的领域。

目前,智能座舱的明星产品是2019年高通发布的骁龙8155芯片,是全球首个采用7nm工艺的汽车芯片。

高通8155座舱平台一经问世便被称为“车规级芯片天花板”,也成为衡量一款智能车科技水平高低的标尺。在当今智能汽车市场,如果没有8155的支持,座舱系统将极大减少对潜在车主的吸引力。而车企“言必称8155”的景象,也像极了智能手机时代争抢高通芯片首发机会的旧事。

2021年底,高通再次发布了全球首个5nm汽车芯片——骁龙8295,相比8155的8TOPS算力,8255芯片AI算力达到30TOPS、GPU性能提升2倍、3D渲染能力提升3倍,增加了集成电子后视镜、机器学习视觉、乘客监测以及信息安全等功能,一颗芯片可带11块屏。

目前来看,高通智能座舱芯片沿袭智能手机芯片的优势。从2014年推出第一代骁龙620A以来,高通已发布四代智能座舱芯片,芯片制程由28nm升级至5nm。

高通如此迅速的将目前最先进的5nm制程工艺芯片完成车规级验证引进到汽车领域,掀起了智能汽车时代高端芯片新的较量,最先进制程的芯片将不再只是消费级电子产品的专属。

除了座舱芯片外,高通的Snapdragon Ride自动驾驶平台的核心SoC也基于5nm制程打造,并集成了高性能CPU、GPU和AI引擎等核心组件,最高算力可达700TOPS。

在自动驾驶时代,“CPU+GPU+XPU”的异构主控SoC芯片将逐渐成为主流,算力正在快速攀升。

在自动驾驶芯片领域,英伟达、Mobileye最新的自动驾驶芯片均采用7nm制程工艺,而特斯拉自研的自动驾驶芯片采用了三星14nm制程。前不久,供应链传出特斯拉HW4.0芯片将转投台积电制造,采用4nm/5nm工艺打造。

以Mobileye EyeQ5芯片为例,该芯片采用了7nm FinFET工艺,单颗算力为24TOPS。而同样是7nm制程的英伟达Orin芯片,单颗的算力达到了256TOPS,几乎达到了前者的10倍。

CES2022器件,Mobileye发布了三颗自动驾驶芯片,其一是面向L4级自动驾驶的芯片EyeQ Ultra,另外两颗是面向L2级自动驾驶的芯片EyeQ6L和EyeQ6H。

EyeQ Ultra是一颗更高算力的自动驾驶芯片,基于5nm制程打造,具备12核、24线程CPU,同时还有两个通用计算加速器和两个CNN加速器,其AI性能能够达到176TOPS。EyeQ Ultra预计将在2025年实现量产上车。EyeQ6系列两款芯片都将基于7nm制程打造,在算力性能和尺寸等方面进行了提升,预计2024年实现量产。

另一边,英伟达在SoC芯片方面,从Parker、Xavier、Orin到还未量产的Thor,在算力、功耗、工艺先进性上不断提升,持续领先高阶自动驾驶。

英伟达的Orin,是7nm高算力芯片的代表,于今年3月官宣量产,该芯片一经推出就获得了比亚迪、理想、蔚来、奔驰、沃尔沃、现代、奥迪等大批主机厂选用。

而英伟达下一代 SoC芯片——Thor,集成了770亿晶体管,单片算力能够达到2000TOPS的性能怪兽,算力达到了现款产品Orin的近8倍,预计将在2025年左右量产。制程工艺暂时还未透露,不过根据推测大概将采用台积电的4nm工艺。

由于性能的强大,Thor可同时为自动泊车、智能驾驶、车机、仪表盘、驾驶员监测等多个系统提供算力,将自动驾驶、信息娱乐等功能划分成不同的任务区间,同时运行,互不干扰。

将芯片算力从几百TOPS一下子“卷”到2000TOPS级的雷神Thor,明确传达出英伟达不会被限定在自动驾驶,还会覆盖智能座舱领域,实现汽车智能化技术的“大一统”。事实上,这也符合汽车电子电气架构从分布式向集约式,中央集中架构发展的技术趋势。

此外,安霸最新AI域控制器芯片CV3系列,恩智浦新一代 S32 系列车用处理器,三星最近同意供应现代汽车Exynos Auto V920娱乐芯片等,也将采用台积电5nm工艺。

而联发科更是“一鸣惊人”,计划推出采用3nm制程的“天玑车载平台”。据了解,“天玑车载平台”将采用3nm制程打造,包含了用于驱动8K、120Hz HDR屏幕的MiraVision显示技术,能够兼容“多个原生HDR摄像头”的图像信号处理单元,可以通过联发科的APU技术为汽车提供一定程度的ADAS辅助驾驶功能,此外还能外挂联网模块,从而实现WiFi7、5G网络、GPS,甚至是卫星联网能力。

除了行业大厂之外,本土SoC已进展至7nm,地平线、黑艺麻智能、芯驰科技、芯警科技都发布了相关产品。其中,芯擎科技自研的“龙鹰一号”作为国内首款车规级7nm芯片近日宣布首发上车,该芯片拥有8核CPU、14核GPU,以及8 TOPS AI算力的独立NPU,最多可支持7屏高清画面输出和12路视频信号接入,并在行业内率先配备双HiFi 5 DSP处理器。

今年4月,黑芝麻智能推出首款自研的7nm芯片武当C1200,基于行业先进工艺,确保算力、功耗、成本能够更好平衡。

地平线CTO黄畅在2022全球AI芯片峰会的演讲中透露,征程6芯片将采用7nm工艺,到征程7或征程8时,地平线的工艺制程将走在行业前列。

纵览汽车芯片产业格局,过往把持车用半导体市场的主要为恩智浦、英飞凌、意法半导体、瑞萨电子等传统汽车芯片大厂。但随着ADAS、自动驾驶技术的兴起,智能汽车对于计算和数据处理能力的需求暴增,让本来就对这块市场有兴趣的科技公司又有了进击的理由。

传统车用芯片虽然标榜高可靠度与稳定性,但考虑到自动驾驶的长期发展,汽车处理器芯片所需要的运算效能一定要提升,先进制程成为不可或缺的关键。

综合来看,目前采用7nm制程的汽车芯片中,已经有不少的产品已经进入量产,主要是智能座舱或自动驾驶芯片,比如英伟达Orin、特斯拉第二代FSD芯片、骁龙8155、芯擎科技“龍鷹一号”等。目前的一些5nm制程汽车芯片大部分仍处于研发当中,或逐渐进入量产阶段,比如高通第四代座舱芯片骁龙8295、高通骁龙Ride自动驾驶平台的核心SoC、安霸最新AI域控制器芯片CV3系列等等。

此外,为支持汽车芯片厂商,台积电在2022年三季度就推出了针对ADAS和智能数字驾驶舱的汽车芯片的5nm工艺平台“N5A”,符合AEC-Q100、ISO26262、IATF16949等汽车工艺标准。

台积电还计划在2024年推出业界第一款基于3nm的汽车芯片平台“N3AE”,计划在2025年量产3nm汽车芯片。

行业厂商的一系列产品动态和规划都在标明,先进制程汽车芯片开始快速迭代,并进入量产加速期。

Chiplet,备受汽车行业瞩目

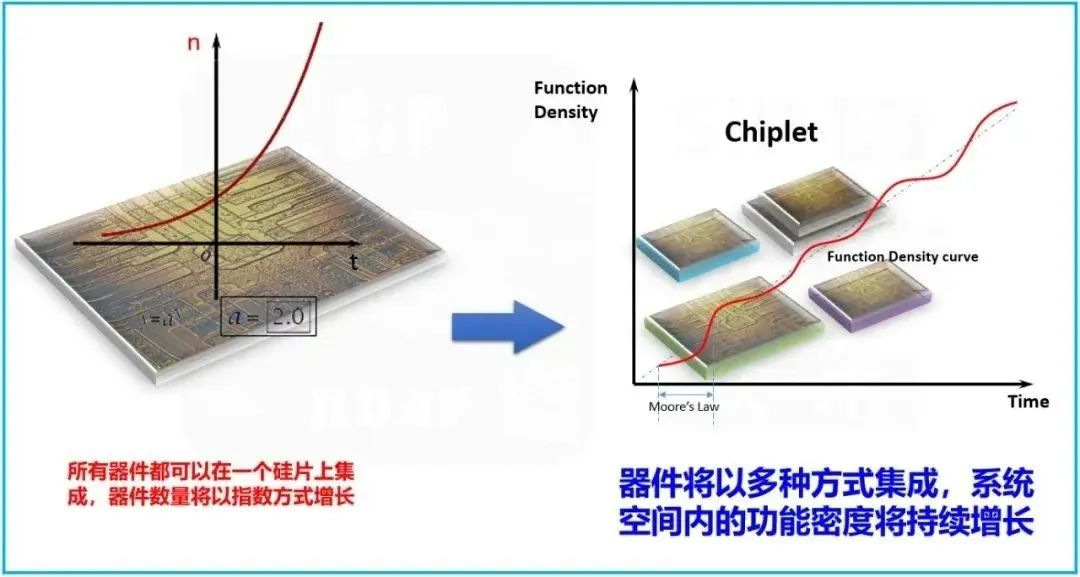

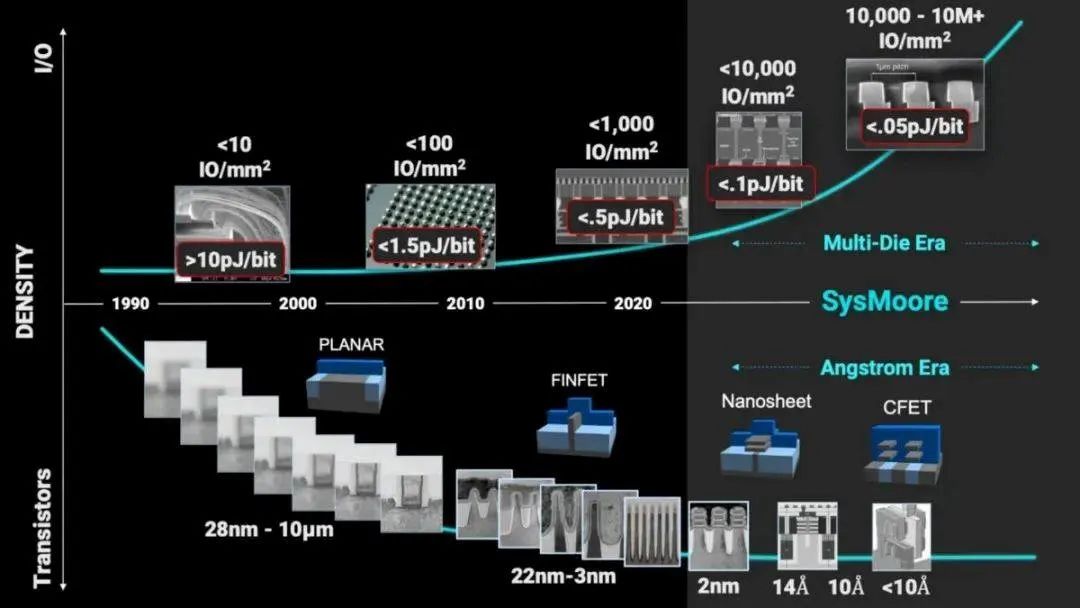

然而,随着先进制程迭代到5nm、3nm,摩尔定律逐渐趋缓,先进制程的开发成本及难度日益提升。

同时,也并不是所有的芯片厂商都可以像英伟达、高通那样通过多个规模化的应用市场来平摊高昂的先进制程工艺芯片的研发成本。

对此,包含汽车芯片在内的半导体行业开始拓展新的技术路线试图延续摩尔定律,而如今被视为“救命稻草”的Chiplet概念也由此提出。

Chiplet也称作“芯粒”或“小芯片”,它是将原本一块复杂的SoC芯片,从设计时就按照不同的功能单元进行分解,然后每个单元选择最适合的制程工艺进行制造,再通过先进封装技术将各个单元彼此互联,就像“乐高积木”一样封装为一个SoC芯片。

简而言之,Chiplet旨在将芯片性能与芯片工艺解耦,从而解决芯片设计中面临的复杂度大幅提升问题,以及先进制程中面临的高成本、低良率问题。

在Chiplet的系统级架构设计下,通过2.5D/3D堆叠等先进封装技术,使用10nm工艺制造出来的芯片可以达到7nm芯片的集成度,其研发投入和一次性生产投入则比7nm芯片的投入要少的多。

此外,模块化的芯粒可以减少重复设计和验证环节,降低芯片的设计复杂度和研发成本,加快产品的迭代速度。同时,降低对先进工艺制程的依赖,对于车载应用市场来说,本身也是一种降本策略。

目前汽车电子是Chiplet技术的主流应用方向之一。

智能汽车电子电气架构从分布式ECU到集中式多域控制器,再到未来的中央计算平台演进,Chiplet技术具备独特的优势。

上文提到,随着汽车产业智能化和网联化程度的不断提高,汽车自动驾驶和智能座舱采用了复杂的SoC芯片,计算/感知/执行都需要更快的数据传输能力给予支撑,而Chiplet可以大幅简化汽车芯片迭代时的设计工作和车规流程,同时增加汽车芯片的可靠性。

从需求端来看,有行业人士指出,由于不同车企的产品定位差异,实际上对于芯片的性能要求并不相同。

但现实情况是,市面上能拿到的芯片,都是标准化产品。车企只能在功能定义、软件算法层面进行差异化的开发。同时,产品路线图必须与芯片厂商保持一致。此外,为了拿到最新一代产品的首发,车企往往还需要支付不菲的费用。

尤其是随着中央计算架构的逐渐到来,平台要实现的功能非常复杂,集成度持续处于不断提升的特点,这意味着通用芯片不足以承载不同车企的需求定义。

因此,对于汽车行业来说,Chiplet是定制汽车SoC的一种新方式。最重要的是,这种方式可以让车企重新获得架构控制权,并决定计算平台需要如何扩展。

在成本方面,相比于直接生产SoC,使用小芯片生产有助于提升晶圆面积利用率,且小芯片可以重复利用,从而降低产品总设计、验证和制造成本。此外,采用Chiplet技术后,各大厂商可以专注于自己的芯粒和IP,省去多余的IP费用。

以AMD为例,通过Chiplet的设计思路,除了能够降低40%的制造成本,还可以更加灵活地销售服务器芯片,根据需要添加和移除小芯片,并能针对不同的功能选项制定不同芯片的价格区间。

众所周知,特斯拉在全球率先启用AMD的座舱计算平台方案(Ryzen APU和基于RDNA 2架构的GPU),后者便是Chiplet技术应用的排头兵,从2015年就开始布局相关技术产品落地。

去年,AMD正式发布了采用RDNA 3架构的新一代旗舰GPU,这是该公司首度在GPU产品中采用Chiplet技术,拥有多达580亿个晶体管,每瓦特性能提升了54%,并且提供高达61TFLOP的算力。

而这只是第一步。按照计划,AMD将寻求在芯片设计方面更符合客户喜好的产品,比如,基于Chiplet技术,客户可以灵活配置第三方IP,尤其是汽车智能化的需求不断释放,未来异构集成的模式,或许会成为市场主流。

看到这个机会的,还有英伟达。英伟达此前推出的NVIDIA NVLink-C2C,这是一种超高速的芯片到芯片、裸片到裸片的互连技术,支持定制裸片与NVIDIA GPU、CPU、DPU、NIC和SoC之间实现一致的互连。

借助先进封装技术,NVLink-C2C互连链路的能效最多可比PCIe Gen 5高出25倍,面积效率高出90倍,可实现每秒900GB乃至更高的一致互联带宽。

“为应对摩尔定律发展趋缓的局面,必须开发小芯片和异构计算。“站在英伟达的角度,这家已经在自动驾驶赛道占据先发优势的芯片巨头,同样觊觎市场规模巨大的跨域市场。

比如,英伟达去年亮相的“超级汽车芯片Thor”,单颗芯片算力达到2000TFLOPS,并通过多颗芯片的NVLink-C2C互连来支持多域计算,以分离自动驾驶等关键安全功能和信息娱乐等功能的处理。

而英伟达与联发科的联姻,更是将Chiplet进一步推向舞台中央。

今年5月,英伟达与联发科宣布,双方将共同为新一代智能汽车提供解决方案,合作的首款芯片锁定智能座舱,预计2025年问世,并在2026年至2027年投入量产。

在这款芯片设计上,联发科将开发集成英伟达GPU芯粒的SoC,搭载NVIDIA AI和图形计算IP,基于Chiplet实现主芯片与GPU芯粒间高速互连。

能看到,Chiplet技术的出现,也意味着汽车芯片除了聚焦先进制程外,通过架构创新实现算力跨越也已成为可能。

汽车行业的各方似乎都在为Chiplet造势。Tier1和OEM正在寄希望于Chiplet可以实现下一代具有差异化的车辆平台。在产业链上下游企业的共同推动下,Chiplet正在不断扩大其商业应用版图。

写在最后

过去几年, 汽车芯片从通用型、分散化的单一功能芯片快速转向集成化的多功能SoC芯片,SoC几乎成了智能汽车行业皇冠上的明珠。

在这个趋势下,汽车芯片也“精益求精”,一方面在先进工艺制程上大有追平消费芯片之势;另一方面,瞄准Chiplet技术寻求“另辟蹊径”。

对于汽车芯片供应商来说,继续选择单芯片、更先进制程工艺,还是选择Chiplet方案,是一个战略抉择。而如何选对方向则考验着企业的判断力。

本文转载自“半导体行业观察”微信公众号,作者:L晨光;智通财经编辑:汪婕。

扫码下载智通APP

扫码下载智通APP